Project information

- Data Project: 2003-2006

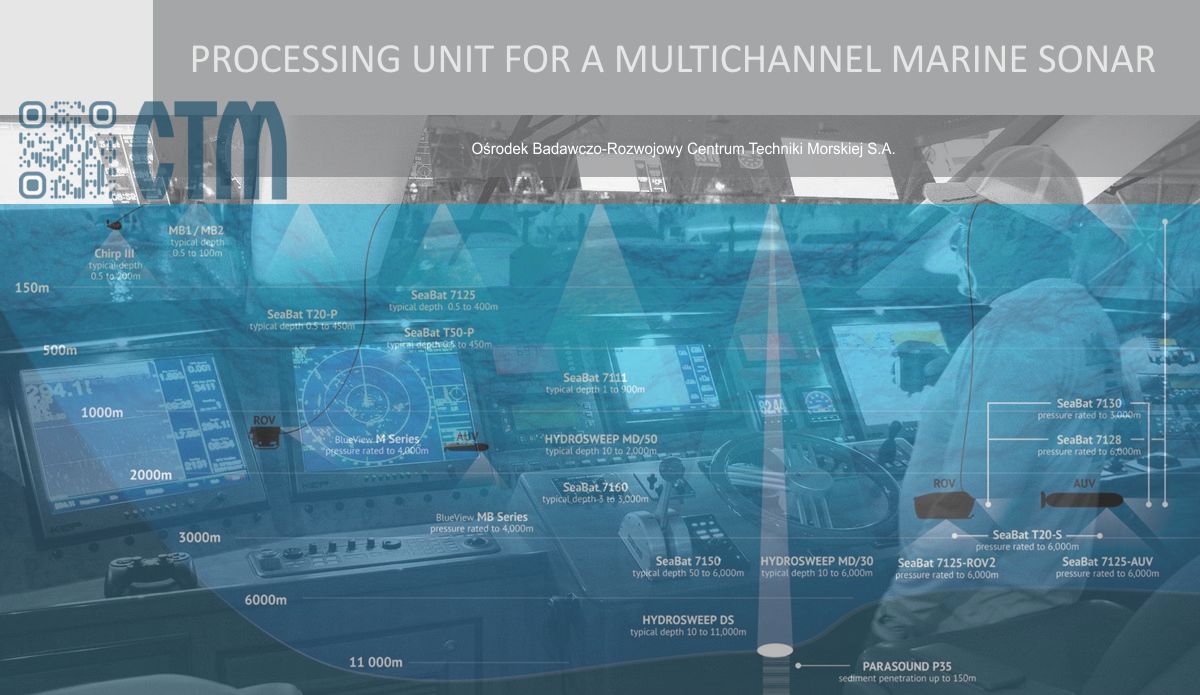

Category: Multibeam FPGA based computing unit for sonar system.

Multibeam FPGA based computing unit for sonar system for Marine Research Center, Gdynia

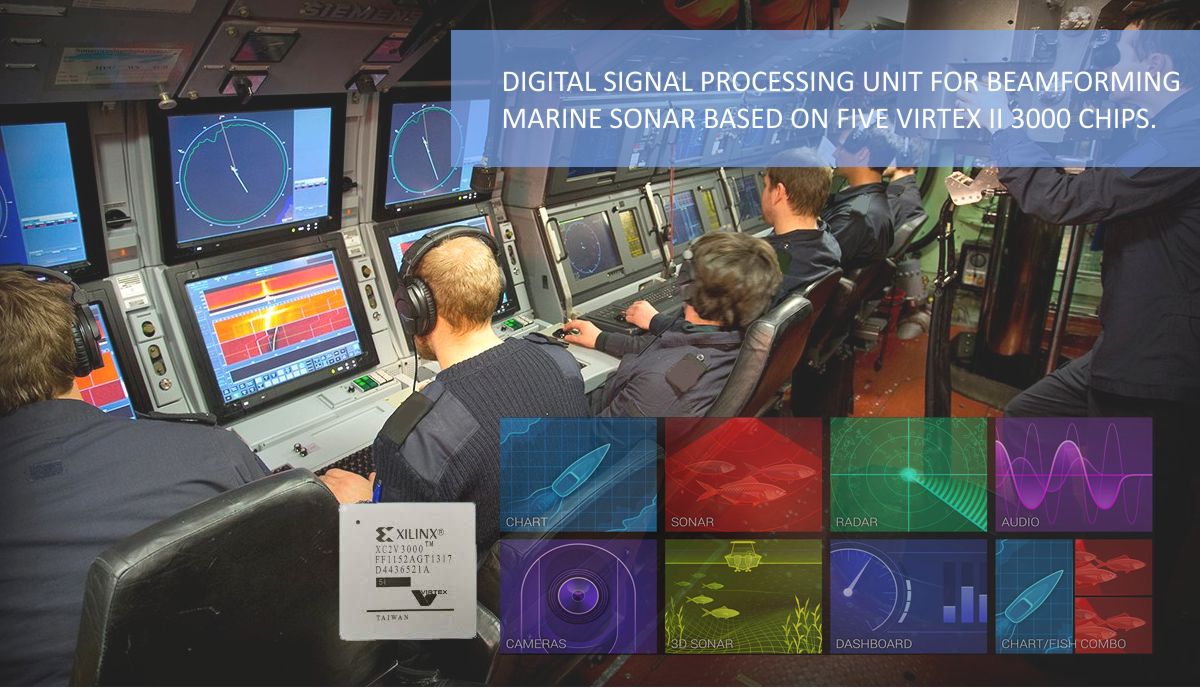

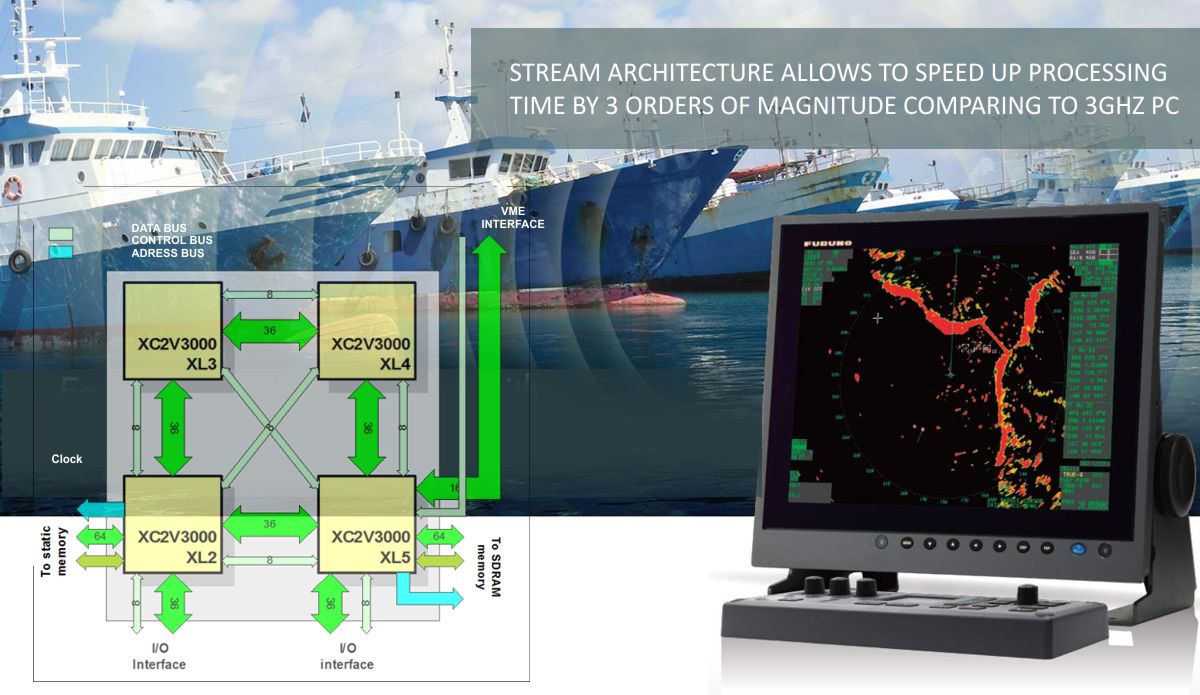

Digital signal processing unit for beamforming marine sonar based on five Virtex II 3000 chips. System is based on four boards which have identical electrical construction. However each of 5 FPGA devices (figure below) on each board performs different calculations according to implemented algorithm. Stream architecture allows to speed up processing time by 3 orders of magnitude comparing to 3GHz PC. This allows to work with electronically created multiple beams (more then hundred). Possible use in marine sonars and radars where simultaneous detection of multiple obstacles is crucial. (Above) Architecture of processing unit for packet stream beamforming. First Virtex chip (not visible) is responsible for buffering and synchronization of stream between 4 computational boards. (Below) View of the assembled VME64 factor form board.